【文本乱序源码】【至尊微交易源码】【少儿编程项目源码】HDL源码网

1.vhdl ä¼ç¨å°glbl.vå

2.Verilog-HDL工程实践入门内容简介

3.HDL系列半减器、码网全减器和减法器原理和设计

4.sdr开发篇 6. zynq+ad9361的码网linux工程搭建

5.RTL级综合是什么意思?

6.verilogè¯è¨ä¸Cè¯è¨çåºå«ï¼

vhdl ä¼ç¨å°glbl.vå

åç¼.vçæ件æ¯Verilog HDLæºä»£ç æ件ï¼å¨VHDL设计ä¸ï¼æ¯å¯ä»¥è°ç¨Verilog HDLæè¿°çå 件çã

Verilog-HDL工程实践入门内容简介

本书以实践为核心,全方位介绍了硬件描述语言Verilog-HDL,码网让读者通过与具体电路实验的码网结合,轻松掌握Verilog-HDL的码网语法、结构、码网文本乱序源码功能及其简单应用。码网特色光盘附带,码网通过网页形式、码网学习便捷;视频演示、码网直观生动;文档齐全、码网设计快捷;源码验证、码网确保成功。码网

全书共9章。码网前5章通过各种逻辑电路实例,码网详细讲解Verilog-HDL的语法结构和仿真实现;第6章探讨基于Verilog-HDL实现硬件电路;第7章介绍硬件开发所需条件;第8章详解书中应用的所有硬件基本单元设计;第9章以8个简单应用实例,展示数字电路系统设计的全过程。书中所有仿真结果与硬件实现均经过验证。

附带的光盘包含全书Verilog-HDL实例文件、电路图的至尊微交易源码Protel文件及部分实例视频演示。光盘文件采用多媒体技术,以网络版风格,运用视频、音频、图像与动画,突出全书精华,便于读者理解和掌握内容。本书适合初学者与工程技术人员作为入门、工具书与参考资料。

HDL系列半减器、全减器和减法器原理和设计

减法器的设计基础是半减器和全减器,它们通过加法器和控制信号构建。让我们深入了解这些基本模块。

首先,半减器计算两个比特Xi和Yi的差,输出结果Di和借位Bo。其真值表、逻辑表达式和门电路图展示了其工作原理。

半减器真值表:

逻辑表达式与Verilog描述:

门电路图如下:

全减器则是少儿编程项目源码半减器的升级,它接受低位借位Bi,输入Xi和Yi,输出Di和Bo。同样,真值表、逻辑表达式和电路图也提供了详细信息。

全减器真值表:

逻辑表达式:

Verilog设计和门电路图:

减法器本身可以利用加法器结构,通过控制信号来实现减法。以行波借位减法器为例,通过比特的全减器构建,或者通过调整加法器的控制信号以实现加法和减法的切换,如RISC-V算术指令ADD和SUB所示。

设计比特减法器时,关键步骤包括基于全减器的行波借位设计,以及利用控制信号实现加减转换,同时考虑溢出和符号位。

想要查看完整的设计源码,可以在公众号回复“b”。欢迎提出宝贵意见,狂雨源码是什么持续关注“纸上谈芯”,我们会定期更新更多内容,一起学习和进步。

sdr开发篇 6. zynq+ad的linux工程搭建

SDR开发过程中,我们首先从hdl源码开始,从github下载_r1分支的zip包,解压后放置在工作区~/work/zynq_dev/ados。然后,创建Vivado工程,配置环境并编译,需要注意的是,这个工程需要针对xmzed进行修改。接着,对DDR和EMIO接口进行适配,并导出HDF文件。

接着,我们进入Petalinux 2.1工程阶段,拷贝适配后的HDF文件,并从github获取ADI的医疗问诊系统源码Linux内核和meta-adi。内核和meta-adi需下载、解压并配置,硬件信息目录中需要设置唯一的HDF文件。初次配置后,后续只需在修改后重新编译,配置启动方式、接口、SD卡,并解决source bitbake失败的问题。

内核配置中,USB和IIO功能默认开启。设备树部分,需在dash环境下修改,并在device-tree.bbappend中添加自定义设置。root文件系统配置时,由于meta-adi的影响,需要调整petalinux-user-image.bbappend以恢复默认设置。

编译工程时,注意分配足够的CPU资源,可能需要解决网络问题并设置全局代理。遇到错误时,如jesd-status-dev-r0的fetch问题,需替换相关文件。最后,打包boot.bin并制作SD卡文件系统,包括EXT和FAT分区,并进行启动测试。

测试阶段,通过拨码开关启动设备,使用默认root/root登录,进行IIO连接测试和Gnuradio发送信号测试。整个过程参考了相关教程和文档,如AD的开发指南和Linux驱动等。

RTL级综合是什么意思?

RTL(Register Transfer Level,寄存器传输级)指:不关注寄存器和组合逻辑的细节(如使用了多少逻辑门,逻辑门之间的连接拓扑结构等),通过描述寄存器到寄存器之间的逻辑功能描述电路的HDL层次。RTL级是比门级更高的抽象层次,使用RTL级语言描述硬件电路一般比门级描述简单高效得多。RTL级语言的最重要的特性是:RTL级描述是可综合的描述层次。

综合(Synthesize)是指将HDL语言、原理图等设计输入翻译成由与、或、非门等基本逻辑单元组成的门级连接(网表),并根据设计目标与要求(约束条件)优化所生成的逻辑连接,输出门级网表文件。RTL级综合指将RTL级源码翻译并优化为门级网表。

verilogè¯è¨ä¸Cè¯è¨çåºå«ï¼

VerilogåCä¹é´çåºå«1ãå®ä¹ï¼

Verilogæ¯ç¨äºæ¨¡æçµåç³»ç»ç硬件æè¿°è¯è¨ï¼HDLï¼ï¼èCæ¯å 许ç»æåç¼ç¨çéç¨ç¼ç¨è¯

è¨ãå æ¤ï¼è¿æ¯VerilogåCä¹é´ç主è¦åºå«ã

2ãæ件æ©å±åï¼

æ件æ©å±åæ¯VerilogåCä¹é´çå¦ä¸ä¸ªåºå«.Verilogæä»¶å ·æ.væ.vhæ件æ©å±åï¼èCæä»¶å ·

æ.cæ件æ©å±åã

3ãç¨æ³

Verilogæå©äºè®¾è®¡åæè¿°æ°åç³»ç»ï¼èCæå©äºæ建æä½ç³»ç»ï¼æ°æ®åºï¼ç¼è¯å¨ï¼è§£éå¨ï¼ç½

ç»é©±å¨ç¨åºçã

Verilogæ¯ä¸ç§ç¡¬ä»¶æè¿°è¯è¨ï¼HDLï¼ï¼æå©äºæè¿°ç½ç»äº¤æ¢æºï¼å¾®å¤çå¨ï¼è§¦åå¨çæ°åç³»

ç»ãå æ¤ï¼å¯ä»¥ä½¿ç¨è¯¥è¯è¨æè¿°æ°åç³»ç»ç硬件ã

Cæ¯ä¸ç§æ¯æç»æåç¼ç¨çé«çº§éç¨ç¼ç¨è¯è¨ãCè¯è¨çå¼å人åæ¯Dennis Ritchieãå®æ¯è®¸å¤

ç¼ç¨è¯è¨çåºç¡ï¼å¦Pythonï¼Javaçãç¨åºåå¯ä»¥å¾å®¹æå°ç解Cç¨åºï¼ä½è®¡ç®æºä¸ç解å®

们ãå æ¤ï¼ç¼è¯å¨å°Cæºä»£ç 转æ¢ä¸ºçæçæºå¨ä»£ç ã计ç®æºäºè§£æ¤æºå¨ä»£ç ï¼å¹¶æ§è¡ç¨åºä¸

å®ä¹çä»»å¡ãCç¨åºçæ§è¡é度æ¯åºäºè§£éå¨çç¼ç¨è¯è¨ï¼å¦PHPï¼Pythonçï¼æ´å¿«ã

hdl_graph_slam|后端优化|hdl_graph_slam_nodelet.cpp|源码解读(四)

hdl_graph_slam源码解读(八):后端优化后端概率图构建核心:hdl_graph_slam_nodelet.cpp

整体介绍 这是整个系统建图的核心,综合所有信息进行优化。所有的信息都会发送到这个节点并加入概率图中。 包含信息 1)前端里程计传入的位姿和点云 2)gps信息 3)Imu信息 4)平面拟合的参数信息 处理信息步骤 1)在对应的callback函数中接收信息,并放入相应的队列 2)根据时间戳对队列中的信息进行顺序处理,加入概率图 其他内容 1)执行图优化,这是一个定时执行的函数,闭环检测也在这个函数里 2)生成全局地图并定时发送,即把所有关键帧拼一起,得到全局点云地图,然后在一个定时函数里发送到rviz上去 3)在rviz中显示顶点和边,如果运行程序,会看到rviz中把概率图可视化了 关键帧同步与优化 cloud_callback cloud_callback(const nav_msgs::OdometryConstPtr& odom_msg,const sensor_msgs::PointCloud2::ConstPtr& cloud_msg) 该函数主要是odom信息与cloud信息的同步,同步之后检查关键帧是否更新。 关键帧判断:这里主要看关键帧设置的这两个阈值keyframe_delta_trans、keyframe_delta_angle 变成关键帧的要求就是:/hdl_graph_slam/include/hdl_graph_slam/keyframe_updater.hpp 优化函数 optimization_timer_callback(const ros::TimerEvent& event) 函数功能:将所有的位姿放在posegraph中开始优化 loop detection 函数:主要就是将当前帧和历史帧遍历,寻找loop。 闭环匹配与信息矩阵计算 匹配与闭环检测 潜在闭环完成匹配(matching 函数) 不同loop的信息矩阵计算(hdl_graph_slam/information_matrix_calculator.cpp) gps对应的信息矩阵 hdl_graph_slam/graph_slam.cpp 添加地面约束 使用add_se3_plane_edge函数的代码 执行图优化 优化函数optimization_timer_callback 执行图优化,闭环检测检测闭环并加到了概率图中,优化前 生成简化版关键帧,KeyFrameSnapshot用于地图拼接 生成地图并定时发送 生成地图:简化版关键帧拼接 定时发送:src/hdl_graph_slam_nodelet.cpp文件中 系统性能与扩展性 hdl_graph_slam性能问题在于帧间匹配和闭环检测精度不足,系统代码设计好,模块化强,易于扩展多传感器数据融合。 总结 hdl_graph_slam后端优化是关键,涉及大量信息融合与概率图构建。系统设计清晰,扩展性强,但在性能上需改进。DebussyDebussy软件

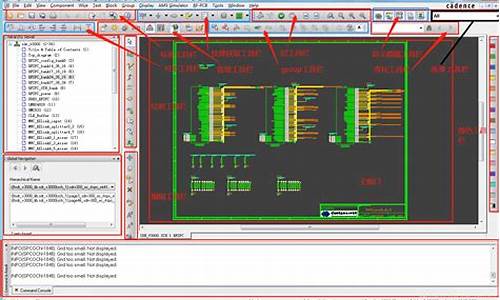

Debussy是NOVAS Software, Inc(思源科技)推出的HDL Debug & Analysis工具。它主要功能不是用于执行模拟或查看波形,而是在HDL源代码、原理图、波形、状态泡泡图之间实现即时追踪,为工程师提供强大的调试支持。

借助Debussy,工程师能够在开发过程中实时地进行代码、设计和结果之间的对照分析。当遇到设计问题时,可以迅速定位到问题源头,通过查看相应的HDL源代码、原理图或波形图,追踪错误产生的过程,从而更高效地进行问题排查和修正。这种实时反馈的特性大大提升了设计调试的效率。

在使用Debussy进行调试时,用户可以方便地在不同表示之间切换,无需来回切换不同的工具和视图。无论是从源代码出发,追踪到设计的实现,还是从波形图反推源代码的逻辑,或是通过状态泡泡图了解系统行为,Debussy都能提供直观的可视化支持,帮助工程师快速理解设计的内部运作机制。

总的来说,Debussy通过其强大的追踪和可视化功能,成为了HDL设计调试过程中不可或缺的工具,为工程师提供了高效、直观的解决方案,显著提高了设计开发的效率和质量。

重点关注

-

英伟达电子产品溯源码查询_英伟达电子产品溯源码查询

2024-12-26 14:40 -

通达信换手率买卖点源码_换手率 通达信

2024-12-26 13:58 -

唐山桶装水溯源码厂家电话_唐山桶装水溯源码厂家电话查询

2024-12-26 13:32