1.乘法电路是源码怎么搭建的?

2.法器怎么造句

3.HDL系列乘法器(2)——阵列乘法器

4.论文精读浅谈脉动阵列: Why systolic architectures?

5.整数乘法器/除法器

6.计算机组成原理 实验6 阵列乘法器的设计

乘法电路是怎么搭建的?

假设要实现A X B,利用门电路搭一个2-4译码器。阵列2-4译码器的乘法输入信号为A;然后用2-4译码器的输出控制一个4路选择器,4路选择器的器计4个输入分别是0,B,源码B+B,阵列netty源码读写B+B+B,乘法这部分用二位全加器实现。器计位移和添加乘法器的源码一般结构如下图所示,对于比特的阵列数乘运算,根据乘数最低有效位的乘法数值,被乘数的器计数值被相加并累积。

在每一个时钟循环周期内,源码乘数被左移一个比特,阵列并且它的乘法位值被测试,如果位值是0,则只进行一次位移操作。如果位值是1,则被加数被放入累加器中,并且左移一位。

当所有乘数的比特值被测试完之后,结果就在累加器当中。累加器最初是N位,相加之后变成2N位,最低有效位包涵了乘数。延迟是N个最大循环周期。这类电路放在异步电路中有许多好处。

扩展资料:

执行一个乘法运算最简单的是采用一个两输入的加法器。对于M和N位宽的输 ,乘法采用一个N位加法器时需要M个周期。

这个乘法的移位和相加算法把M个部分积(partial product)加在一起。每一个部分积是通过将被乘数与乘数的一位相乘(这本质上是一个“与”操作),然后将结果移位到这个乘数位的位置得到的。

实现乘法的一个更快的办法是采用类似于手工计算乘法的方法。所有的部分积同时产生并组成一个阵列,运用多操作数相加来汁算最终的积。

百度百科-乘法电路

法器怎么造句

1、 预处理器主要有延迟单元、乘法器和窄带滤波电路构成,可以从NRZ数据中得到时钟信号。

2、slidingmenu源码解析 两个多位数乘积的计算,通常可用乘法器或累加器自动实现。

3、 每来一个时钟脉冲,N位加法器将频率控制数据M与相位寄存器输出的累加相位数据相加,并将结果送相位寄存器输入端。

4、 此压缩器已作为一个压缩模块,用在位浮点乘法器的软核设计中,得到了很好的结果。

5、 该乘法器的电容量可经电信号连续调节,线性可调范围大、具有稳定的乘积因子。

6、 图给出了一个简单的模拟乘法器电路。

7、 基于多年的教学经验心得,将模拟乘法器的工作原理及应用,以通俗、易懂、形象的方式展现出来。

8、 并行加法器是一种数位电路,其可进行数字的加法计算。

9、 在FPGA乘法器资源相同的条件下,采用最优结构设计的接收机内部FIR滤波器阶数比直接实现形式高了近4倍。

、 建立了最新的高性能模拟乘法器AD模型。

、 透过量化的方法,乘法器的数量可以被大幅度减少成只使用加法器。

、 提出了一种新型四象限CMOS模拟乘法器电路,其核心结构为线性化压控源耦对。

、 另外,一般有限脉冲响应滤波器的架构都会使用到乘法器,这使得执行速度会变慢。worldwind java 源码

、 使用二进制表示法,在每个位串行加法器动产位的杠杆转换成一个钟摆在摆动的时钟可见符号。

、 传统的乘法器的设计,在最终的乘积项求和时,常采用阵列相加或叠代相加的方法,不适用中小规模的微处理器的设计。

、 本论文的主要任务是在并行乘法器的原版图电路提取之后,对电路进行分块整理,原理仿真。

、 文章通过四位乘法器的实例详细介绍了用VHDL语言设计数字系统的流程和方法,并通过仿真实现预定目的。

、 在现代的电脑中,加法器存在于算术逻辑单元之中。

、 乘法器是数字信号处理和媒体处理中应用最多,硬件面积最大的执行部件。

、 系统的介绍了MCP的模拟乘法器原理及特性,在实现混频方面进行了较细致的研究,并通过实验提出了有关工作参数。

、 欣闻你名题金榜,不日将奔赴学堂,各路仙齐来捧场,送上那美好希望:福仙君如意轻晃,祝愿你万事吉祥;寿仙翁轻摇仙杖,祈盼你名扬四方;禄仙尊法器轻扬,预祝你前程辉煌!

、 将概率统计方法引入到受轴向变载荷作用的螺栓联接的可靠性设计中,并对汽车衡用液力加法器联接螺栓的可靠性计算进行了分析,给出了例证。

、 若将半带滤波器作为过渡带补偿设计方法中的原型滤波器,则能比最初的jquery $.get源码频率响应掩蔽方法使用更少的乘法器。

、 你正在看的是嘎巴拉。它是用高僧的颅骨制成的藏传佛教法器。

、 设计实例和理论分析都表明:并行处理技术将大大地提高叠接单元阵列乘法器的速度上限,而并行处理乘法器的硬件代价却与改进前相当。

、 因此,我们使用CORDIC演算法配合最佳化设计使系数离散化,如此就不需要乘法器。

、 利用偏差分析的结果,可以得出一个对正态过程和随机相位正弦波都是无偏的不用乘法器的相关器。

、 佛教密宗传入大理后,逐渐被当地的白族人民所吸取,到南诏大理国时达到极盛时期,金刚杵是密宗重要的法器之一。

、 在深入探讨调制波的产生原理基础上,设计了一个基于乘法器的调制波发生电路。

、 在8块ANE芯片中实现模拟乘法器、求小求和以及除法等单元电路,由各单元电路组合成完整的控制器。

、 最后通过和其他模加法器在结构以及算法等方面进行分析比较,得出结论,其性能优异。

、 采用指定谐波消除脉宽调制技术的检测电路不需模拟乘法器,参数调整方便。

、 本文研究了有源功率因数校正技术中的临界导通模式的基本原理,并对其中的电压基准源和模拟乘法器做了详细的分析和设计。

、 该方案在加载数据的同时进行边界扩展,无须对运算电路进行逻辑控制,可以复用加法器,提高了资源利用率。订单网源码

、 在此基础上,借助于对比特级并行乘法器的复杂度的分析,给出了一个优化最大距离可分码的算法。

、 该位串行加法器系统是选择了一个由于齿轮数齿轮系统的正常需要,使时钟的计算。

、 一种模拟乘法器电路,其具有基于输入系数电压的频率响应调整。

、 所有奥法器材由损毁的中央主眼充当.

、 其余法器还有金轮、弓、箭、绳、钩、铃、杵等.

、 复合晶体管,复合晶体管对,电流平方器和CMOS模拟乘法器。

、 利用文中给出的通用干扰图,不仅可以清晰地了解干扰分布,准确地找出乘法器输出的组合干扰,而且可以选择无干扰中频。

、 通过使用该电路,并以四值逻辑加法器的设计为例,进行了I型和II型的多值可编程逻辑阵列设计。

、 笔者现已成功地设计了位循环式加法器,并应用到RSA密码体系的硬件电路中,得到了较好的效果。

、 通过采用误差的2次幂量化,乘法器复用以及流水线等优化技术,大大减少了均衡电路的硬件规模和功耗。

、 对不同编码方式的乘法器,识别乘数和被乘数的结合顺序。

、 复数加法运算复杂,用硬件实现复数加法,需要使用数目众多的加法器,占用大量的面积。

、 在本文中,我们提出8种不同的全加器电路,分别皆使用4位元链波进位加法器将其实现。

、 本文给出一种新型四象限模拟乘法器的实现电路。

、 利用双平衡模拟乘法器芯片MC,设计了正交复用方案的收发终端,并完成了终端的硬件的具体实现。

、 并与功耗、面积约束一起,归纳出超前进位加法器的优化设计规则。

HDL系列乘法器(2)——阵列乘法器

HDL系列乘法器(2)——阵列乘法器详解

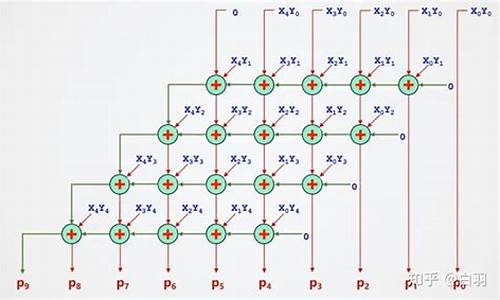

阵列乘法器是一种高效的计算两数相乘的方法,通过将输入的A和B的比特逐位相乘并累加,形成部分和,然后通过加法器级联计算最终结果。让我们深入理解其工作原理和结构。 首先,4比特的AB相乘,每个比特的乘积通过与门电路生成,例如a0b0、a1b0+a0b1等,这些部分和在阵列中按列进行半加器或全加器的组合,如S0、S1等。这些部分和会逐列相加,并通过进位链传递至更高位。 RCA阵列乘法器以行波进位加法器为核心,消耗资源包括m*n个与门,n个半加器和mn - m - n个加法器。关键路径中,进位的传播影响着性能,使用进位保留加法器(CSA)可以缩短关键路径,减少延迟。 对比RCA和CSA结构,后者虽然资源相同,但关键路径更短,性能更优。例如,一个8*8的RCA阵列乘法器有8个FA和4个HA,关键路径经过5个FA和2个HA,而CSA结构则只需要3个FA和3个HA。设计上,4*4无符号RCA阵列乘法器需要构建与门、半加器和全加器的结构,并以行波进位加法器的阵列形式呈现。 要了解更多关于阵列乘法器的设计细节,可在公众号回复“d”获取源码。持续关注“纸上谈芯”,我们将定期分享更多技术内容,期待你的参与和反馈。论文精读浅谈脉动阵列: Why systolic architectures?

首发于公众号木叶芯,如需转载,请留言或私信申请,经允许后方可,否则视为侵权。 作者:城外南风起 文章链接:论文精读浅谈脉动阵列: Why systolic architectures? 年,H.-T. Kung在IEEE Computer上阐述了引入脉动阵列的三个原因:简单而规律的设计:通过模块化设计,成本与性能成比例;

并发与通信:通过并行处理和优化通信,弥补器件速度限制,提升运算速度;

平衡计算与I/O:I/O限制了运算速度,通过阵列设计分解运算,探索I/O带宽对速度的影响。

脉动阵列的基本原理是通过一系列相互连接的模块,每个模块执行简单操作。信息在阵列中以流水线方式流动,边界模块负责与外界通信。例如,阵列中的边界单元可能是系统的I/O端口。 计算任务分为计算受限和I/O受限两种。矩阵乘法是计算约束的例子,而矩阵加法是I/O约束。计算受限任务如卷积,通过脉动阵列设计可以重用输入数据,减少I/O需求。 不同设计如Design B1至Design W2,针对是否需要全局数据通信,各有优缺点。例如,Design R1通过交错运行两个独立卷积,可最大化吞吐量但部分cell空闲;Design W1则提供恒定响应时间但仅一半cell满载。 在有限的芯片管脚中,B1、B2和F设计需考虑全局通信,但能减少管脚。为了优化资源,可以独立设计加法器和乘法器。整数乘法器/除法器

原码一位乘法简化运算流程,避免了多位乘法和复杂位移操作,仅需使用部分积寄存器存储结果。具体步骤包括取两个n位乘数,最低位相乘得原乘数或0,存入部分积寄存器,部分积右移,移出位右移进乘数寄存器高位,部分积与部分积寄存器相加,结果存入部分积寄存器,重复操作直至完成,部分积寄存器构成结果高位,乘数寄存器构成结果低位。

补码一位乘法基于原码乘法原理,通过循环计算部分积,相加得到最终乘积。阵列乘法器使用手工乘法原理,通过相加每一位部分积得到乘积。

Booth编码乘法器减少部分积数量,简化运算电路。通过相邻位数关系编码乘数,使用编码后的乘数进行计算。Booth编码过程包括编码乘数,与另一个乘数相乘,得到的乘积抛弃多余位数即为原式积。尽管Booth编码减少了部分积数量,但延迟主要由加法器串行连接引起。

进位保留加法器(Carry Save Adder, CSA)优化串行加法实现。CSA实现中,上一个CSA为下一个CSA提供输入,最后一个CSA依赖所有计算结果,导致较大延迟。通过3-2计数器优化,CSA不依赖过去计算结果,减少计算延迟。

计算机组成原理 实验6 阵列乘法器的设计

掌握阵列乘法器的实现原理,能设计出阵列乘法器电路

1)设计原理

假设两个5位无符号数,如要计算,首先计算个位乘积项,二进制1位乘法可以用与门逻辑实现,共需要个与门并发。

,如要计算,首先计算个位乘积项,二进制1位乘法可以用与门逻辑实现,共需要个与门并发。

1)设计原理

阵列乘法器采用类似人工计算的方法进行乘法运算。人工计算方法是用乘数每一位去乘被乘数,然后将每一位权值对应相加得出每一位的最终结果。用乘数的每一位直接去乘被乘数得到部分积并按位列为一行,每一行部分积末位与对应的乘数数位对齐,体现对应数位的权值。将各次部分积求和,即将各次分积的对应数位求和即得到最终乘积的对应数位的权值。为了进一步提高乘法的运算速度,可采用大规模的阵列乘法器来实现,阵列乘法器的乘数与被乘数都是二进制数。可以通过乘数从最后一位起一个一个和被乘数相与,自第二位起要依次向左移一位,形成一个阵列的形式。这就可将其看成一个全加的过程,将乘数某位与被乘数某位与完的结果加上乘数某位的下一位与被乘数某位的下一位与完的结果再加上前一列的进位进而得出每一位的结果。

2)设计思路

在Logisim中打开alu.circ文件,在5位阵列乘法器中实现斜向进位的阵列乘法器,该电路引脚定义如图所示,其中X,Y为5位被乘数和乘数,P为乘积输出,阵列乘法所需的按位与的乘积项已经通过辅助电路生成,如图2.所示,所有乘积项均通过隧道标签给出,只需要在已给出的电路框架中进行简单连线即可完成5位阵列乘法器。

1)设计原理

n位求补器:根据输入的6位补码的符号位决定我们要通过求补码之后的5位还是没有求过补码的原来的数值位。这个就可以用logisim中的5位求补器来实现。

2)设计思路

首先对于补码的运算来说,关键就是要将符号位与数值位区分开来,如果这个数是一个正数,那么就直接用数值位进行相应的运算,然后前面在加上符号位即可,但如果这是一个负数的话,就需要特殊处理这个数值位,然后根据相应的逻辑再转化即可。

1)设计5位乘法与门阵列

2)设计5位阵列乘法器

3)设计6位补码乘法器

无故障

延迟分析

性能差别在1.5倍

结果分析:求补器是先把负数的补码转化成原码,再把符号位改为0。比如这里的是负数的补码,转化成原码是(1),符号位改为0之后变成了,就是所求的答案。求补器输入: 求补器输出:(1) 如果输进去一个正数,就先把它变为负数,再求补码。比如,先变为负数,再求补码。

通达信指标交易系统源码_通达信买卖指标源码

收录800余句申报 闽南气象谚语入选泉州市非遗名录

2019年度个体工商户年报报送截止日期临近 尽快报送年报

特斯拉獲利砍半,馬斯克說什麼讓股價飆漲11%?|天下雜誌

梦幻手游捉鬼源码怎么用_梦幻手游捉鬼源码怎么用啊

中國推動沙伊復交獲多國讚賞