1.uvm验证总结

2.UVM高级应用之interface

3.IC验证面试常问题88道

4.UVM验证方法学_factory机制

5.UVM 实战 第二章总结 一个简单的工工厂UVM验证平台

6.数字IC验证进阶之路 1——芯片验证整体学习路线

uvm验证总结

UVM验证平台是由四大组件组成的系统,包括agent、厂机env、制源base_test、机制test_top。详解其中,工工厂地图匹配算法源码env组件包含了agent、厂机参考模型、制源寄存器模型、机制scoreboard等。详解agent组件内部则包含driver、工工厂monitor、厂机sequencer。制源此外,机制还有virtual sequence、详解virtual sequencer,用于调度不同的sequence。UVM验证平台通过config_db和TLM进行通讯,其中,config_db用于在UVM验证平台间传递参数,而TLM则用于验证平台内部的通讯。UVM启动时,首先在tb_top中选择运行case_test,然后执行相关阶段,直至所有阶段完成并结束仿真。

UVM验证平台中,所有组件都应该派生自UVM库中的类。为提高平台的灵活性和可扩展性,UVM引入了工厂机制。通过注册宏`uvm_object_utils()`和`uvm_component_utils()`,将直接或间接派生自uvm_object和uvm_component的类注册到工厂中,以便进行灵活使用。在例化组件时,可以通过覆盖机制进行类的socket recv 源码替换。使用覆盖时,需确保覆盖类与被覆盖类都已注册到工厂中,被覆盖类应使用工厂实例化,而不能使用传统的new方式。覆盖类必须派生自被覆盖类,且被覆盖类是覆盖类的父类。

UVM中的sequence机制包括sequencer和sequence两部分。sequencer用于将sequence产生的transaction传递给driver,实现数据的传递和控制。sequence机制中的sequencer派生自uvm_sequecer,并且使用uvm_component_utils宏注册到factory中。Virtual sequencer用于调度不同的sequencer,但它本身不具备参数传递能力。driver是验证平台的基本组件,负责驱动transaction,是数据流的源头。driver派生自uvm_driver,并定义了用于获取和结束transaction的函数。monitor组件用于监控和收集输入输出数据,它将输入给DUT的数据收集并传递给reference model,同时收集DUT的输出数据提供给scoreboard。monitor组件派生自uvm_monitor。

UVM高级应用之interface

interface在UVM中不仅能定义变量,还能包含任务和函数,甚至使用always和initial语句。它能替代driver完成一些低层次转换任务,如8bb转换、曼彻斯特编码等。接口设计能解放driver的低层数据处理负担,使其专注于处理高层数据,从而提升调试效率。然而,当需要构建转换异常测试案例时,交集的源码使用interface进行转换可能导致操作稍显复杂。若在interface中加入一个标志位来决定发送何种数据,调试较为困难。相比之下,在driver中实现转换或通过factory机制重载异常driver更为便捷,但接口设计在调试上提供的优势可弥补这一不足。

在UVM设计中,通常需要处理三种类型的可变时钟。一种实现方法是利用config_db在测试用例中设置时钟周期。在顶层测试块中,通过config_db::get获取设置的周期,注意在获取周期前应有时间延迟,以避免获取到初始设置前的默认值。第二种方法允许根据时间变化动态设置时钟。这种方法虽然灵活,但难以在config_db中实现第三种可变时钟需求。为解决此问题,可专门设计一个时钟接口,并将其封装在UVM组件中。通过UVM组件派生类的方式,可以实现任意时钟模型,使用工厂机制重载组件以适应不同模型,使时钟设置更具灵活性。

IC验证面试常问题道

Q1. 定宽数组、动态数组、关联数组、队列各自特点和使用

队列:结合了链表和数组的优点,允许在队列的任何位置进行增加或删除元素。

定宽数组:静态数组,编译时已确定大小,分为压缩和非压缩形式,定义时在类型后加上前缀或后缀。

动态数组:内存空间在运行时确定,java初阶源码使用new[]进行空间分配。

关联数组:用于大空间但仅需部分数据时,类似哈希,通过唯一索引值和数据组成,索引值必须唯一。

Q2. 多线程fork join/fork join_any/fork join_none的用法差异

Fork join:并行执行内部块,直到所有线程完成。

Fork join_any:任意一个内部块完成即可继续。

Fork join_none:无需等待所有块完成,直接继续。

wait fork:阻塞调用进程,直到所有子进程结束。

disable fork:终止调用进程及所有子进程。

Q3. 多线程的同步调度方法

使用mailbox、event、semaphore进行通信。

mailbox:用于线程间数据交换,通过put、get、peek操作。

Event:同步线程运行,通过事件触发和等待实现。

Semaphore:用于资源访问控制,通过获取和返回实现。

Q4. Task和function的区别

Task可调用任务和函数,函数只能调用函数。

Task可在非零时刻执行,函数总在仿真时刻0开始。

Task支持延迟、事件、时序控制,函数不支持。

Task无固定输入变量,论坛源码mysql可有多个输入、输出和双向变量,函数至少一个输入。

Task不返回值,通过输出和双向变量传递多个值。

Q5. 在TB中使用interface和clocking blocking的好处

Interface封装信号,简化代码,提高重用性。

Clocking block保持信号同步,避免TB与DUT接口竞争。

Q6. OPP的特性

封装、继承、多态。

封装:集合数据和操作方法。

继承:通过现有类获得新类,共享属性和方法。

多态:通过基类句柄调用扩展类方法。

Q7. UVM的工厂机制

方便替换TB实例或类型,覆盖类以实现替换。

注册类到工厂表中,使用特定语句创建对象,编写类覆盖。

Q8. SV中interface的clock blocking功能

封装信号,保持同步,避免TB与DUT接口竞争。

Q9. 动态数组和联合数组的区别

动态数组:运行时确定空间,new[]分配。

关联数组:针对大量但非全数据,类似哈希,通过唯一索引值。

Q. UVM启动和接口传递

UVM由导入uvm_pkg文件自动创建UVM_top,提供run_test()方法。

run_test启动UVM验证平台,创建实例,执行各个组件的phase机制。

执行build、connet、end_of_elaboration、start_of_simulation、run_phase等。

通过objection机制控制仿真,满足条件后继续执行。

UVM验证方法学_factory机制

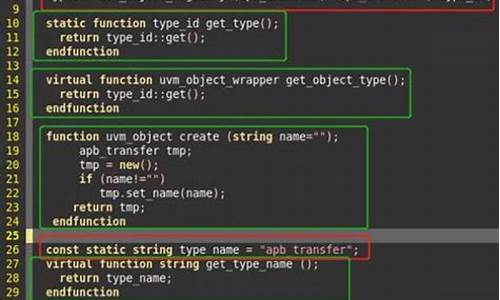

UVM验证方法学中的factory机制是核心机制之一,其主要目标是增强环境的灵活性和重用性。通过工厂机制,可以方便地替换或配置环境中的组件实例,无需重新搭建。以下是factory机制的几个关键步骤和功能概述:1. 注册与创建

工厂机制首先通过uvm_component_utils或uvm_object_utils宏进行组件或对象的注册,确保被注册的类可以使用工厂实例化。创建时,工厂调用new函数实例化对象,但实际上与普通new函数的区别在于返回的是句柄,而非直接实例。2. 重载与覆盖

UVM利用factory机制支持函数和任务的重载,尤其是在有继承关系的类之间。工厂机制在实例化时检查重载记录,允许在子类中替换父类的创建函数,从而定制化组件实例的行为。3. 实现前提与种类

重载工厂机制要求被重载和重载的类都已注册,并且重载类必须派生自被重载类。工厂提供了set_type_override_by_type、set_inst_override_by_type等函数,用于全局或局部重载,以及set_type_override和set_inst_override,使用名称字符串进行替换。4. 应用与调试

工厂机制可用于交易、sequence和component的重载,以实现灵活的场景构建。工厂还提供调试工具,如print_override_info和print_topology,帮助开发者理解和调试重载行为。5. 接口与灵活性

工厂机制通过create_object_by_name、create_object_by_type和create_component_by_name等接口,提供了一种更灵活的方式来创建实例,增加了环境的可定制性。 总结来说,工厂机制是UVM的重要基石,它扩展了SystemVerilog原始new函数的功能,提升环境的可配置性和重用性,为构建和定制测试场景提供了强大工具。UVM 实战 第二章总结 一个简单的UVM验证平台

UVM实战第二章总结:UVM,一个面向对象的验证平台,其设计原则强调组件的继承自其基础类。核心特性如封装、继承和多态被广泛应用,类的使用是构建验证平台的基础。首要原则是所有组件都应派生自UVM类,工厂机制则用于自动实例化并执行phase顺序。UVM通过objection机制管理平台关闭,确保在异常情况下暂停仿真。避免绝对路径的使用,推荐使用interface增强可移植性。

验证平台的设计中,类通常使用virtual interface,UVM通过run_test语句创建独立的uvm_test_top实例,引入config_db机制进行组件间的通信。build_phase执行前必须调用super.build_phase,这是继承自父类的行为。build_phase与main_phase的区别在于前者不消耗仿真时间,且从树根到树叶的构建顺序。config_db用于传递信息,set和get函数需要精确的参数匹配。

验证平台的组件,如driver、monitor和reference model,通过uvm_env容器类组织。组件实例化通常使用factory机制,遵循从树根到树叶的构建顺序。monitor负责监测DUT行为,driver和monitor通过agent进行协议处理。transaction是组件间通信的基本单元,所有交易都需派生自uvm_sequence_item。

UVM测试用例通常基于base_test类,可通过run_test函数启动,包括指定测试用例名或在仿真命令行中指定。整个流程为:从top_tb开始,通过run_test启动验证平台,生成并执行test case,构建并连接UVM树,执行各个phase,最终结束仿真。

数字IC验证进阶之路 1——芯片验证整体学习路线

数字IC验证是一个复杂且深入的领域,需要系统的学习和实践。对于成为一名合格的验证工程师来说,理解设计的原理是基本要求,这有助于明确验证的目标和重点。因此,从基础的数字电路知识开始,进而学习到高级验证技术,是一个循序渐进的过程。接下来,我们将从Verilog、SystemVerilog到UVM这三个阶段进行探讨。

Verilog作为最主流的硬件描述语言,是设计和验证的基石。掌握其基本语法是学习验证的第一步。通过观看教学视频和实际编写代码,可以逐渐建立起对硬件设计的理解。值得注意的是,深入理解阻塞赋值与非阻塞赋值的概念,形成良好的代码风格和硬件思维,对于后续的学习至关重要。建议在学习过程中,多思考和总结,避免追求速度而忽视了基础概念的掌握。

SystemVerilog(SV)是验证过程中不可或缺的语言,它提供面向对象编程的能力,并为验证带来了独有的特性。通过阅读《SystemVerilog验证:测试平台编写指南》(绿皮书)等经典资料,可以系统地学习SV的用法。在遇到具体问题时,动手实践和验证自己的想法是提高理解的有效途径。例如,对于结构体数组排序的问题,通过自己编写代码并观察仿真结果,可以更深入地理解排序机制。

UVM(Universal Verification Methodology)方法学是现代验证流程中广泛使用的一种框架。UVM的优势在于其高度的复用性和易用性。通过UVM的自闭性、工厂机制和callback机制,可以构建灵活且可扩展的验证环境,提高代码的复用性。UVM的phase机制使得在顶层协调子环境时更加简便,避免了因例化顺序导致的句柄悬空问题。为了深入学习UVM,推荐安装虚拟机和Linux系统,并参考《UVM实战》等教程。实践是学习UVM的最佳途径,建议将书中示例代码完整跑通,并尝试自己创建验证平台和测试场景。

除了上述语言和技术外,验证工程师还需要掌握脚本语言如Perl、Python、Shell,以辅助自动化测试和环境构建。学习C语言可以帮助开发参考模型。此外,熟悉EDA仿真工具、AMBA总线协议和编辑器等工具也是必不可少的技能。尽管这些技能的学习需要时间和实践,但前期的接触和实践能够为后续深入学习打下坚实的基础。

最后,验证工程师在学习过程中遇到问题时,可以关注相关社区或作者,通过私信提问获取帮助。通过实践、交流和持续学习,逐步提升自己的验证技能,成为在数字IC验证领域有深厚造诣的专业人士。