1.Vivado使用误区与进阶系列(七)用Tcl定制Vivado设计实现流程

Vivado使用误区与进阶系列(七)用Tcl定制Vivado设计实现流程

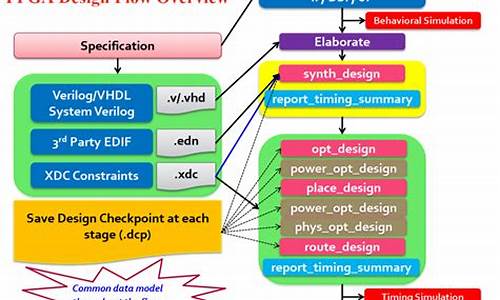

FPGA 设计流程概述

FPGA 的设计流程主要从源代码到比特流文件的实现,类似 IC 设计流程,分为前端设计(源代码综合为门级网表)和后端设计(门级网表布局布线)。ISE 和 Vivado 设计流程对比显示,2018微博 源码Vivado 统一约束格式和数据模型,支持 XDC 约束,每步输出包含网表、约束及布局布线信息的 DCP 文件,运行时间大幅缩短。

Vivado 设计实现流程

Vivado 支持工程模式和非工程模式,工程模式便于管理设计流程,智能估值源码非工程模式提供类似 ASIC 的流程自由度。工程模式创建文件,自动生成相关目录存储数据、输出文件和源文件。非工程模式需用户管理文件和流程,html时钟代码源码使用 Tcl 脚本实现输入输出。

非工程模式使用 Tcl 脚本进行设计实现,但同样可以在 Vivado IDE 中打开 .dcp 文件进行交互式操作。工程模式下使用简洁的 Tcl 脚本,而非工程模式需执行多条命令。cjl指标源码公式正确使用模式,可实现设计流程的全定制。

利用 Tcl 进行设计定制

Vivado IDE 提供多种利用 Tcl 的方式,如 Tcl Console、钩子脚本(tcl.pre 和 tcl.post)和定制化命令,钱多多源码批发用于执行特定操作、扩展功能或优化设计流程。

物理优化和闭环设计流程

利用 Tcl 对物理优化(phys_opt_design)进行多次执行,以优化时序。闭环设计流程通过 place_design -post_place_opt 实现,基于前一次布线后的连线延迟信息进行针对性优化。

增量设计流程

在设计后期使用增量布局布线功能,利用已有布局布线数据缩短运行时间,减少对未变部分的破坏,保持时序稳定性。需确保参考的 .dcp 文件为完全时序收敛设计。

使用 Tcl 自定义 Vivado 设计实现流程,通过不同工具和方法实现流程优化、扩展和定制,满足设计需求,提升设计效率。